Embark: Evaluation of Mapping NLP based Alogrithms into Reconfigurable Computing Kernels

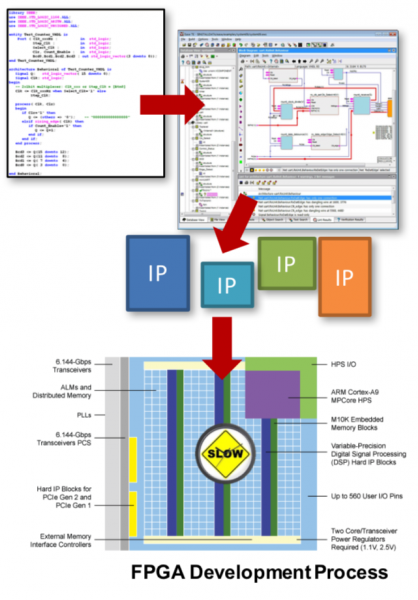

As Field Programmable Gate Arrays (FPGAs) continue to evolve in both capability and resource density, researchers are exploring novel uses to accelerate information extraction applications, such as through Natural Language Processing (NLP). While FPGAs seem to be perfectly suited to process large streams of data and can even organize it to be more efficiently accessed by conventional processing elements like CPUs and GPGPUs, FPGA implementations are challenging to develop for. Moreover, FPGAs suffer from slower clock rates, which must be overcome to warrant its use as more than typical glue logic circuitry. Fortunately, with advancements in high-speed interfaces, integrated DSP hard IP, and on-chip memory densities, FPGAs can leverage pipe lining and parallelism to compensate for these limitations.

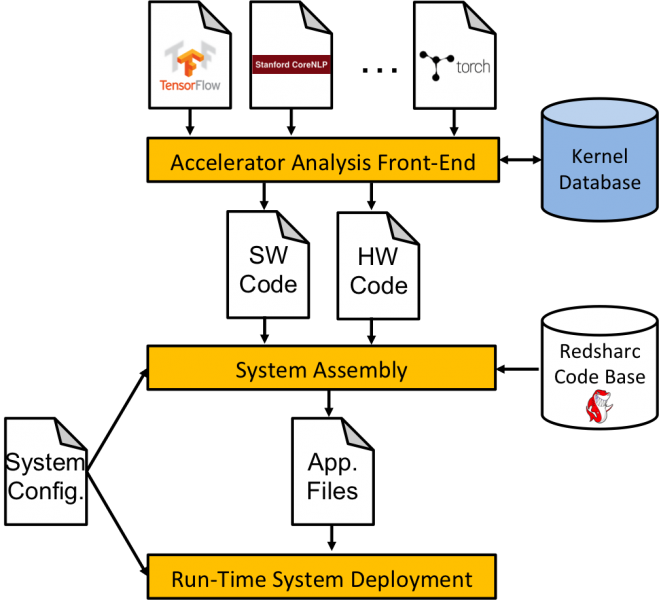

EMBARK provides insight into the feasibility and scalability of information extraction applications to tightly couple FPGA-based heterogeneous and/or cloud computing systems. This includes metrics for performance to overcome slow FPGA clock limitations and resource constraints (on-chip memory, DSP- based floating point units, etc.) as part of pipe lining architecture design trade-offs. In addition, an analysis of the granularity of kernel development necessary to support higher-level composition of compute kernels on-the- fly during algorithm decomposition and mapping, and preliminary supporting data for FPGAs in a Platform-as-a-Service heterogeneous system will be provided.

Cumulatively, this represents a significant step toward a Platform-as-a-Service heterogeneous system, reducing development efforts for FPGA-based systems. The work enabled preliminary data collection and analysis through a prototype system to establish metrics and answer performance and scalability questions regarding the algorithms on such a heterogeneous system.