RHinO: Reconfigurable Hardware in Orbit

Overview

The Reconfigurable Hardware in Orbit (RHinO) project is focused on creating a set of design tools that facilitate and automate design techniques for reconfigurable computing in space, using SRAM-based field-programmable-gate-array (FPGA) technology. These tools leverage an established FPGA design environment and focus primarily on space effects mitigation and power optimization. The project is creating software to automatically test and evaluate the single-event-upsets (SEUs) sensitivities of an FPGA design and insert mitigation techniques. Extensions into the tool suite will also allow evolvable algorithm techniques to reconfigure around single-event-latchup (SEL) events. In the power domain, tools are being created for dynamic power visualization and optimization. Thus, this technology seeks to enable the use of Reconfigurable Hardware in Orbit, via an integrated design tool-suite aiming to reduce risk, cost, and design time of multi-mission reconfigurable space processors using SRAM-based FPGAs.

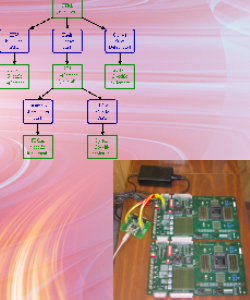

JHDL Backbone

Using the well establsihed JHDL infrastructure, we are adding tools and viewers that allow an FPGA application designer to better consider radiation mitigation and power minimization.

SEU Effects

We are developing a scalable, open API-based SEU emulator, capable of testing configurations. We have also developed a half-latch mitigation tool.

Power

In the power domain, we have developed tools to visualize dynamic power consumption and judge the quality of place and route iterations in terms of power. Future research will be on tools to optimize power utilizing this information.

Self Repair

Our tools are also supporting hooks to allow evolvable algorithm techniques to re-route around hard faults in-orbit.