Mirage: A Security Metrics Driven Obfuscation Design Environment

Project Navigation

Overview

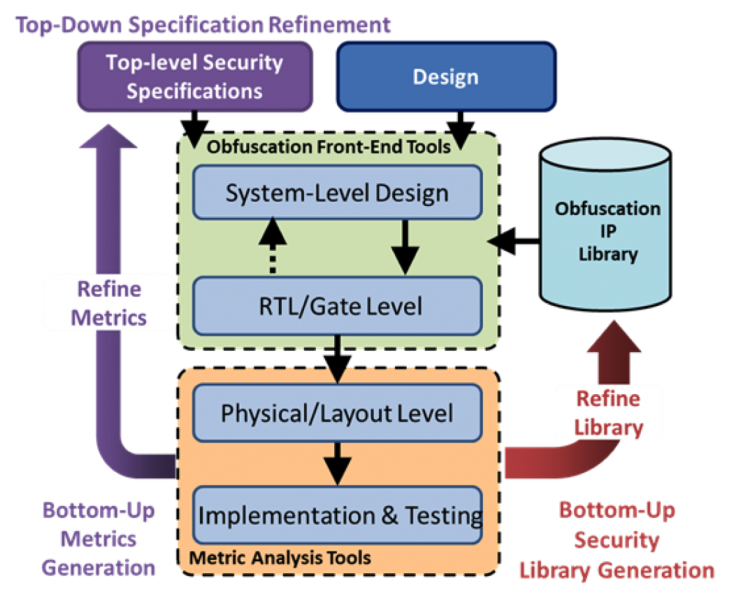

In today’s global marketplace, IP protection is becoming a serious concern in ASIC development. Circuit-level obfuscation is a potentially viable solution, however no common metrics exist to evaluate these techniques and no design tools exist to guide and validate implementation. Mirage utilizes quantitative security and overhead metrics to ascertain which obfuscation techniques provide realistic levels of security and utilizes state of the art design space exploration techniques to select and apply the best techniques for a given circuit.

Mirage is principally composed of a front end Obfuscation Design Space Exploration engine which utilizes feedback from security metrics to drive selection of obfuscation IP and is interoperable with standard ASIC EDA tools. Mirage utilizes Design Space Exploration (DSE) algorithms well suited for large search spaces leveraging intelligent pruning and compositional reasoning. The Security-centric metrics that are applicable to both passive and active obfuscation techniques. Mirage focuses on unified, adversary centric models that are applicable across a range of obfuscation types. In addition to overhead metrics, Mirage also provides techniques for verification of the correct application of the obfuscation.

The material is based on research sponsored by the Air Force Research Labs (AFRL) and the Defense Advanced Projects Agency (DARPA) under agreement number FA8650-18-1-7817. The U.S. Government is authorized to reproduce and distribute reprints for Government purposes notwithstanding any copyright notation thereon. The views and conclusions contained herein are those of the authors and should not be interpreted as necessarily representing the official policies or endorsements, either expressed or implied, of the Air Force Research Labs (AFRL), the Defense Advanced Projects Agency (DARPA), or the U.S. Government. This work is also supported by generous donations from Synopsys and Cadence.

Publications

Similarity-Based Logic Locking Against Machine Learning Attacks

S. D. Chowdhury, K. Yang, and P. Nuzzo, Design Automation Conference (DAC), Jul. 2023.

Unraveling Latch Locking Using Machine Learning, Boolean Analysis, and ILP

D. Chen, X. Zhou, Y. Hu, Y. Zhang, K. Yang, A. Rittenbach, P. Nuzzo, and P. A. Beerel, International Symposium on Quality Electronic Design (ISQED), Apr. 2023.

On the Security of Sequential Logic Locking Against Oracle-Guided Attacks

Y. Hu, Y. Zhang, K. Yang, D. Chen, P. A. Beerel, P. Nuzzo, IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD), Mar. 2023.

TriLock: IC Protection with Tunable Corruptibility and Resilience to SAT and Removal Attacks

Y. Zhang, Y. Hu, P. Nuzzo, P. A. Beerel, Proc. Design Automation and Test in Europe Conference (DATE), Mar. 2022.

Towards a Formal Treatment of Logic Locking

P. A. Beerel, M. Georgiou, B. Hamlin, A. J. Malozemoff, P. Nuzzo, IACR Transactions on Cryptographic Hardware and Embedded Systems (TCHES), pp. 92-114, Feb. 2022.

Fun-SAT: Functional Corruptibility-Guided SAT-Based Attack on Sequential Logic Encryption

Y. Hu, Y. Zhang, K. Yang, D. Chen, P. A. Beerel, P. Nuzzo, Proc. IEEE International Symposium on Hardware Oriented Security and Trust (HOST), Dec. 2021.

ReIGNN: State Register Identification Using Graph Neural Networks for Circuit Reverse Engineering

S. Dutta Chowdhury, K. Yang, P. Nuzzo, Proc. Int. Conf. Computer Aided Design (ICCAD), Nov. 2021.

SANSCrypt: Sporadic-Authentication-Based Sequential Logic Encryption

Y. Hu, K. Yang, S. Nazarian, P. Nuzzo, VLSI-SoC: Design Trends, Springer, pp. 255-278, Jul. 2021.

Enhancing SAT-Attack Resiliency and Cost-Effectiveness of Reconfigurable-Logic-Based Circuit Obfuscation

S. Dutta Chowdhury, G. Zhang, Y. Hu, P. Nuzzo, Proc. IEEE Int. Symp. Circuits and Systems (ISCAS), pp. 1-5, May 2021.

Risk-Aware Cost-Effective Design Methodology for Integrated Circuit Locking

Y. Hu, K. Yang, S. Dutta Chowdhury, P. Nuzzo, Proc. IEEE/ACM Design Automation and Test in Europe Conf. (DATE), pp. 1182-1185, Feb. 2021.

SANSCrypt: A Sporadic-Authentication-Based Sequential Logic Encryption Scheme

Y. Hu, K. Yang, S. Nazarian, P. Nuzzo, Proc. IFIP/IEEE Int. Conf. Very Large-Scale Integration (VLSI-SoC), pp. 129-134, Oct. 2020.

Security-driven Metrics and Models for Efficient Evaluation of Logic Encryption Schemes

Y. Hu, V. V. Menon, A. Schmidt, J. Monson, M. French, and P. Nuzzo, Proc. Int. Conf. on Formal Methods and Models for System Design (MEMOCODE), p. 9, pp. 1-5, Oct. 2019.

System-Level Framework for Logic Obfuscation with Quantified Metrics for Evaluation

V. V. Menon, G. Kolhe, A. Schmidt, J. Monson, M. French, Y. Hu, P. A. Beerel, P. Nuzzo, IEEE Cybersecurity Development Conf. (SecDev), pp. 89-100, Sep. 2019.

Improved Metrics for Obfuscated ICs.

M. Zhu, M. French, and P. Beerel, Government Microcircuit Applications and Critical Technology Conference (GOMACTech), 2018.

Paper | Presentation

People

Leadership

Matthew French

Pierluigi Nuzzo

Peter Beerel

Research Staff

Andrew Schmidt

Benedict Reynwar

Travis Haroldsen

Dong-In Kang

Joshua Monson

Samuel Skalicky

Vivek Venugopalan

Ting-Yuan Sung

Andrew Rittenbach

Young Cho

Research Assistants

Subhajit Dutta Chowdry

Yinghua Hu

Kaixin Yang

Zhiyu Ni

Mutian Zhu

Meghana Thommondru

Joseph Fifty

Manoj Bhavani Sankar Poturaju

Rakibul Hassan

Richard Becker

Rishik Dutta

Sanket Sanjay Shukla

Shervin Roshani Sefat

Uddipt Sharma

Hunain Ali Shamsi

Dake Chen

Yue Hu

Yuke Zhang

Interns

Gaurav Kohle

Dhanush Srinivasa

Collaborators

Georgia Tech Research Institute (GTRI)

Greg Mohler, Sub PI

Galois

Alex Malozemoff, Sub PI

New York University