ISI News

USC Viterbi School of Engineering and Industrial Technology Research Institute to Collaborate on Microelectronics

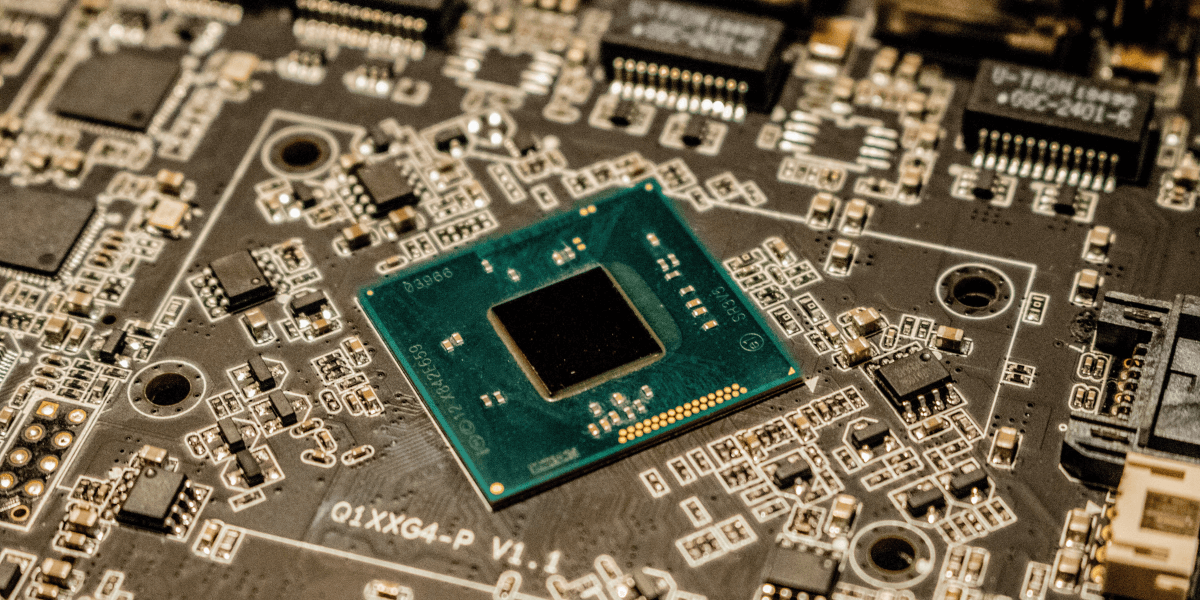

The University of Southern California (USC) and Industrial Technology Research Institute (ITRI) in Taiwan announced their collaboration to advance the field of microelectronics with emphasis in research and development, integrated circuit design, and manufacturing.

USC’s Ming Hsieh Department of Electrical and Computer Engineering (ECE), USC’s Information Sciences Institute (ISI), and ITRI will collaborate on semiconductor research and development in areas of Heterogeneous Integration, Artificial Intelligence, Non-Volatile Memory, Next-Generation Computing and IC Design. USC’s ISI’s Metal Oxide Semiconductor Implementation Service (The MOSIS Service) and ITRI will concentrate on IC design and development service, IP support, and silicon shuttle service. This coordinated research initiative is critical given the increasing global demand for chips.

“ITRI does world class research and their focus is to commercialize, to put their products in major retail stores. Out of all the companies they could have worked with, they chose ISI, because we lead this industry and our team performs robust work,” said Lifu Chang, Director of The MOSIS Service at ISI.

Yannis C. Yortsos, Dean of the USC Viterbi School of Engineering, said, “we are excited that the research teams at USC’s ECE and ISI with strong profiles in artificial intelligence, radio-frequency and millimeter-wave IC designs, analog IP, quantum computing, and optoelectronics can extend their global collaborations with ITRI’s outstanding teams. We look forward to seeing how this R&D collaboration will advance the microelectronic technologies going into applications of great innovations.”

USC has long had expertise in chip design and security. At ISI, The MOSIS Service was founded in 1981 at USC Information Sciences Institute via a DARPA contract to facilitate the first manufacturing projects for fabless organizations. After pioneering the Multi-Project Wafer (MPW) model, MOSIS has also provided services to US Government Laboratories, foreign and domestic corporations, and foreign and domestic universities.

“We are pioneers in the fabrication of microchips. We have three major categories of customers,” details Chang. “The defense industry organizations, who are our very long-time customers. Then the university community; pretty much all American ones have worked with us: UCLA, UC Berkeley, Stanford, MIT, you name it. Then we work with commercial design companies. For example, we expect to sign an agreement with a company in San Diego, California, to provide chips for their significant medical applications.”

Craig Knoblock, the Keston Executive Director of Information Sciences Institute and Vice Dean of USC Viterbi School of Engineering, said “we are strongly encouraged about this collaboration opportunity with ITRI. The MOSIS Service has the leading-edge capabilities to support semiconductor design and manufacturing and we now start to work with ITRI’s focused IP and silicon fabrication development platform. We look forward to seeing the fruition of semiconductor projects that will benefit innovative start-up companies in the US and Taiwan.”

ITRI President Edwin Liu expressed his excitement to see how the partnership will bring new opportunities, using ITRI’s multidisciplinary R&D platforms and MOSIS’ prototyping capacities. “ITRI and USC will collaborate via an institution-to-institution mechanism and build a customer service business model that provides Taiwan’s companies with chip packaging and related downstream services following trial production,” he said.

Over the years, MOSIS has delivered chips for more than 60,000 designs and enabled IC designers to prototype innovative semiconductor designs. The Ming Hsieh Department has provided expertise in chip material and design for a wide variety of applications, with a recent emphasis on design for neural networks and quantum computing. In addition, USC scholars have developed novel methods to test chip integrity.

Published on

Last updated on